# KFG4GH6x4M KFH8GH6x4M KFWAGH6x4M

## 4Gb Flex-OneNAND M-die

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS, AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,

TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL INFORMATION IN THIS DOCUMENT IS PROVIDED

#### ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

- 1. For updates or additional information about Samsung products, contact your nearest Samsung office.

- Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where Product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

**Flex-OneNAND**™, is a trademark of Samsung Electronics Company, Ltd. Other names and brands may be claimed as the property of their rightful owners.

<sup>\*</sup> Samsung Electronics reserves the right to change products or specification without notice.

## **Revision History**

## Document Title Flex-OneNAND Revision History

| Revision No. | History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Draft Date                     | Remark      |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------|

| 0.0          | 1. Initial issue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Aug. 22, 2007                  | Preliminary |

| 0.0          | <ol> <li>Initial issue.</li> <li>Corrected errata.</li> <li>Chapter 2.1 Detailed Product Description revised.</li> <li>Chapter 2.2.2 Definitions revised.</li> <li>Chapter 2.8.3 Device ID Register F001h(R) revised.</li> <li>Chapter 2.8.10 Start Address2 Register F101h(R/W) revised.</li> <li>Chapter 2.8.10 Start Address2 Register F107h(R/W) revised.</li> <li>Chapter 2.8.17 Start Buffer Register F200h (R/W) revised.</li> <li>Chapter 2.8.18 Command Register F220h(R/W) revised.</li> <li>Chapter 2.8.21 Interrupt Status Register F241h(R/W) revised.</li> <li>Chapter 3.1 Command Based Operation revised.</li> <li>Chapter 3.1.2 Load Data Into Buffer Command revised.</li> <li>Chapter 3.4.3 NAND Array Write Protection States revised.</li> <li>Chapter 3.4.3 I Unlocked NAND Array Write Protection State revised.</li> <li>Chapter 3.4.3.1 Unlocked NAND Array Write Protection State revised.</li> <li>Chapter 3.4.3 Socked-tight NAND Array Write Protection State revised.</li> <li>Chapter 3.4.2 Synchronous Read Mode Operation revised.</li> <li>Chapter 3.7.2 Synchronous Read Mode Operation revised.</li> <li>Chapter 3.9 Program Operation revised.</li> <li>Chapter 3.9.1 Cache Program Operation revised.</li> <li>Chapter 3.9.2 Interleave Cache Program Operation revised.</li> <li>Chapter 3.11.2 Erase Suspend / Erase Resume Operation revised.</li> <li>Chapter 3.12 Partition Information (PI) Block(SLC Only) revised.</li> <li>Chapter 3.12.1 PI Block Boundary Information setting revised.</li> <li>Chapter 3.12.1.3 PI Block Access mode entry revised.</li> <li>Chapter 3.12.1.4 PI Update revised.</li> <li>Chapter 3.12.1.5 PI Block Access mode entry revised.</li> <li>Chapter 3.12.1.5 PI Block Program Operation revised.</li> <li>Chapter 3.15.2 Invalid Block Replacement Operation revised.</li> <li>Chapter 3.15.2 Invalid Block Replacement Operation revised.</li> <li>Chapter 6.15 Program Operation Timing tINTW removed.</li> <l< th=""><th>Aug. 22, 2007<br/>Nov. 02, 2007</th><th>Preliminary</th></l<></ol> | Aug. 22, 2007<br>Nov. 02, 2007 | Preliminary |

| 1.0          | <ol> <li>Chapter 7.4 DDP and QDP Description inserted.</li> <li>New Format(font size, color etc.)</li> <li>Corrected errata.</li> <li>Added a comment(Chapter 3.11.1 &amp; 3.12.1.2 &amp; 3.12.1.3 &amp; 3.12.1.4)</li> <li>Chapter 1.0 INTRODUCTION revised.</li> <li>Chapter 2.8.17 Start Buffer Register F200h (R/W) revised.</li> <li>Chapter 3.12.2 PI Block Load Operation revised.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Feb. 04, 2008                  | Final       |

7. Chapter 4.3 DC Characteristics revised.

### 1.0 INTRODUCTION

This specification contains information about the Samsung Electronics Company Flex-OneNAND<sup>TM</sup>, Flash memory product family. Section 1.0 includes a general overview, revision history, and product ordering information.

Section 2.0 describes the Flex-OneNAND device. Section 3.0 provides information about device operation. Electrical specifications and timing waveforms are in Sections 4.0 through 6.0. Section 7.0 provides additional application and technical notes pertaining to use of the Flex-OneNAND. Package dimensions are found in Section 8.0

| Density   | Part No.        | Vcc(core & IO)   | Temperature | PKG        |

|-----------|-----------------|------------------|-------------|------------|

| 4Gb       | KFG4GH6Q4M-DEBx | 1.8V(1.7V~1.95V) | Extended    | 63FBGA(LF) |

|           | KFG4GH6U4M-DIB6 | 3.3V(2.7V~3.6V)  | Industrial  | 63FBGA(LF) |

| 8Gb       | KFH8GH6Q4M-DEBx | 1.8V(1.7V~1.95V) | Extended    | 63FBGA(LF) |

|           | KFH8GH6U4M-DIB6 | 3.3V(2.7V~3.6V)  | Industrial  | 63FBGA(LF) |

| 16Gb(TBD) | KFWAGH6Q4M-DEBx | 1.8V(1.7V~1.95V) | Extended    | 63FBGA(LF) |

|           | KFWAGH6U4M-DIB6 | 3.3V(2.7V~3.6V)  | Industrial  | 63FBGA(LF) |

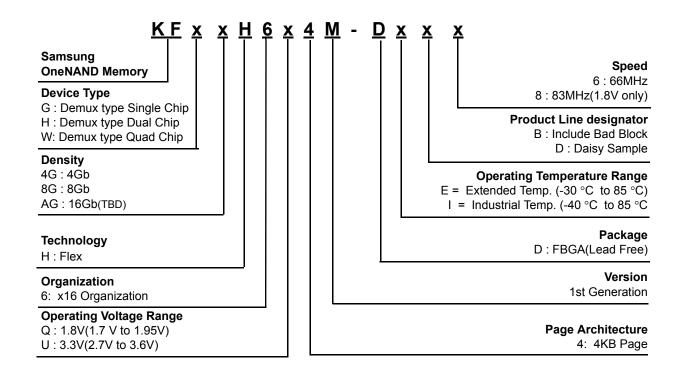

## 1.1 Ordering Information

#### 1.2 General Overview

$\label{eq:Flex-OneNAND} \textit{TM} is a monolithic integrated circuit with a NAND Flash array using a NOR Flash interface.$

The chip integrates system features including:

- · A BootRAM(1KB) and bootloader

- 4KB DataRAM buffers

- A High-Speed x16 Host Interface

- On-chip Error Correction

- On-chip NOR interface controller

This on-chip integration enables system designers to reduce external system logic and use high-density NAND Flash in applications that would otherwise have to use more NOR components.

Flex-OneNAND takes advantage of the higher performance NAND program time, low power, and high density and combines it with the synchronous read performance of NOR. The NOR Flash host interface makes Flex-OneNAND an ideal solution for mobile applications that have large, advanced multimedia applications and operating systems and need high performance.

When integrated into a Samsung Multi-Chip-Package with Samsung Mobile DDR SDRAM, designers can complete a high-performance, small footprint solution.

The device operates up to a maximum host-driven clock frequency of 66MHz / 83MHz for synchronous reads at Vcc(or Vccq. Refer to chapter 4.2) with 4~7-clock latency. Appropriate wait cycles are determined by programmable read latency.

Flex-OneNAND provides for multiple sector read operations by assigning the number of sectors to be read in the sector counter register. The device includes one block-sized OTP (One Time Programmable) area and user-controlled 1st block OTP(Block 0) that can be used to increase system security or to provide identification capabilities.

#### 1.3 Product Features

Difference between 1.8V product and 3.3V product in terms of functions.

|                                     | 1.8V         | 3.3V         |

|-------------------------------------|--------------|--------------|

| Synchronous Read                    | up to 83Mhz  | up to 66Mhz  |

| SuperLoad<br>(Sync. read mode only) | O<br>(83Mhz) | O<br>(66Mhz) |

| Synchronous Write                   | up to 83Mhz  | Async Only   |

| Cache Program                       | 0            | Х            |

| Interleaving Cache Program          | 0            | X            |

| Interleaving Erase                  | 0            | 0            |

| Interleaving Program                | 0            | 0            |

#### **Device Architecture**

· Design Technology:

· Supply Voltage:

· Host Interface:

• 5KB Internal BufferRAM:

NAND Array:

#### **Device Performance**

Host Interface Type:

· Programmable Burst Read Latency:

· Multiple Reset Modes:

· Low Power Dissipation:

Reliable CMOS Floating-Gate Technology

#### System Hardware

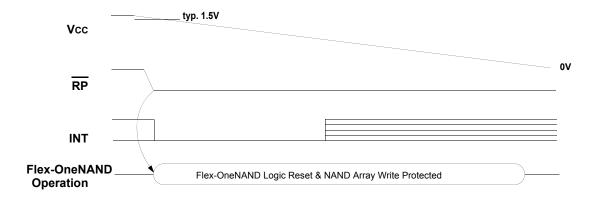

- Voltage detector generating internal reset signal from Vcc

- Hardware reset input (RP)

- · Data Protection Modes

- User-controlled One Time Programmable(OTP) area

- Internal 4bit ECC

- Internal Bootloader supports Booting Solution in system

- · Handshaking Feature

- · Detailed chip information

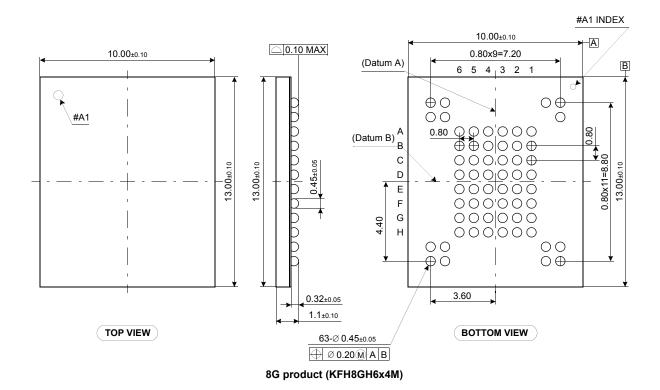

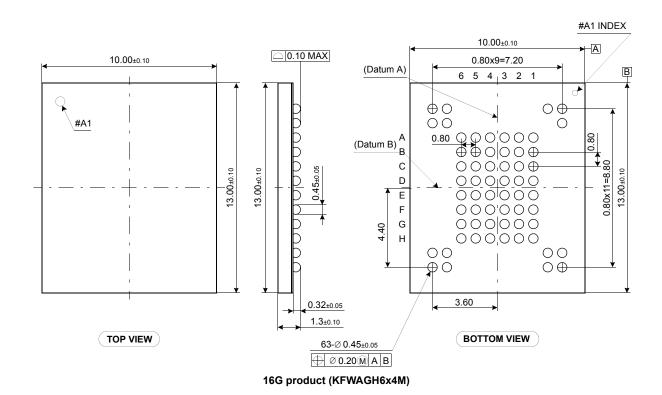

#### Package size

- 4G products

- 8G products

- 16G products(TBD)

M die

1.8V (1.7V ~ 1.95V), 3.3V(2.7V~3.6V)

16 bit

1KB BootRAM, 4KB DataRAM SLC: (4K+128)B Page Size

(256K+8K)B Block Size (64pages)

MLC: (4K+128)B Page Size

(512K+16K)B Block Size (128pages)

#### Synchronous Burst Read

- Up to 66MHz / 83MHz(1.8V only) clock frequency - Linear Burst 4-, 8-, 16-, 32-words with wrap around

- Continuous 1K words Sequential Burst

Synchronous Write (1.8V only)

- Up to 66MHz / 83MHz clock frequency

- Linear Burst 4-, 8-, 16-, 32-, 1K-words with wrap around

- Continuous 1K words Sequential Burst

Asynchronous Random Read

- 76ns access time Asynchronous Random Write

Latency 3,4(Default),5,6 and 7.

1~40MHz: Latency 3 available

1~66MHz: Latency 4,5,6 and 7 available Over 66MHz: Latency 6,7 available.

Cold/Warm/Hot/NAND Flash Core Reset

Typical Power (Single chip),

- Standby current: 10uA@1.8V, 35uA@3.3V

- Synchronous Burst Read current(66MHz): 20mA@1.8V, 30mA@3.3V

- Synchronous Burst Read current(83MHz): 25mA@1.8V

- Synchronous Burst Write current(66MHz/83MHz): 20/25mA@1.8V

- Load current: 50mA@1,8V, 55mA@3.3V - Program current: 35mA@1,8V, 40mA@3.3V

- Erase current: 40mA@1,8V, 40mA@3.3V

- Endurance : 50K Program/Erase Cycles (SLC) 10K Program/Erase Cycles (MLC)

- Data Retention: 10 Years(SLC) /10 Years(MLC)

- Write Protection for BootRAM

- Write Protection for NAND Flash Array

- Write Protection during power-up

- Write Protection during power-down

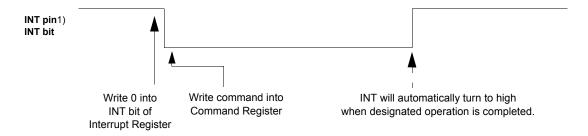

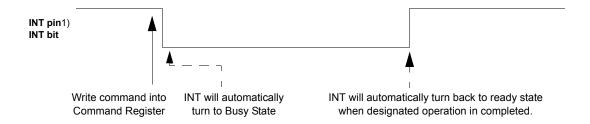

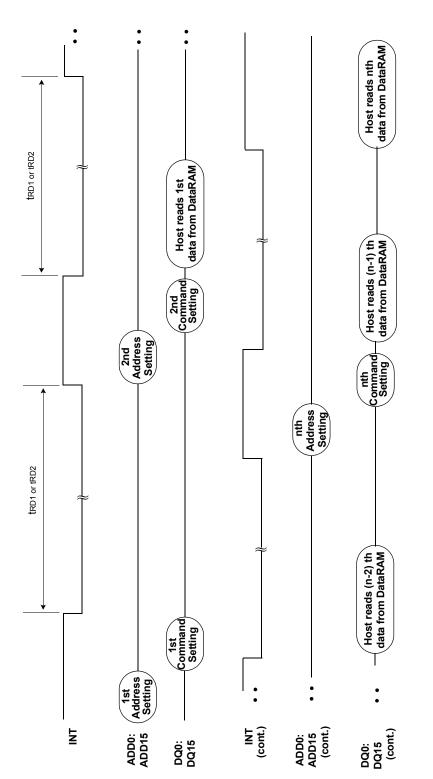

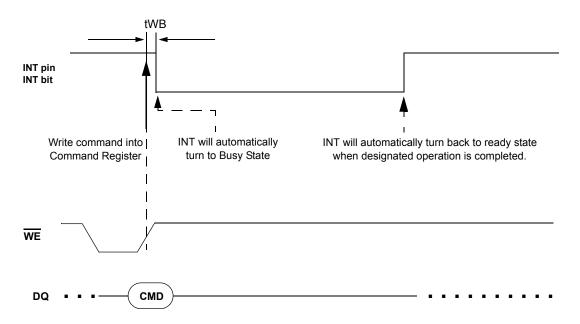

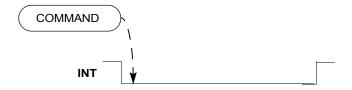

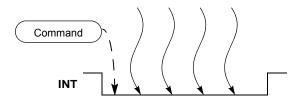

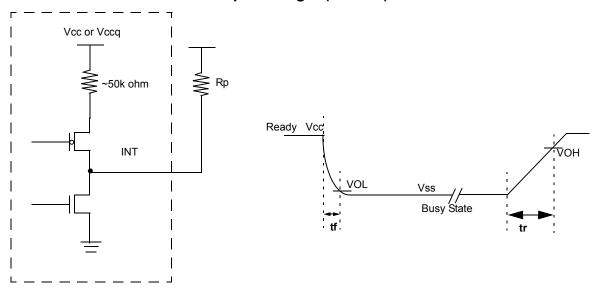

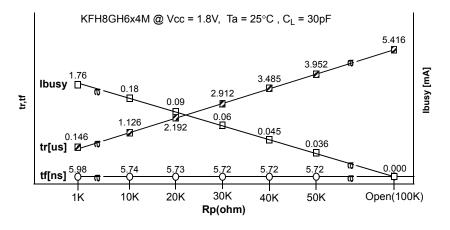

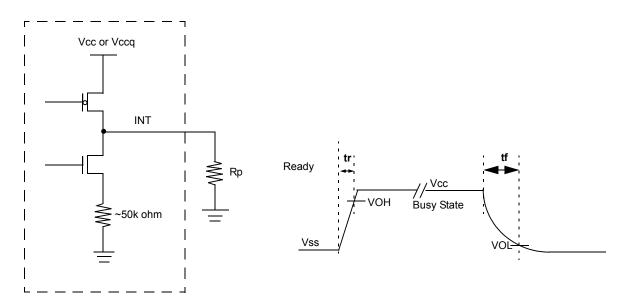

- INT pin indicates Ready / Busy

- Polling the interrupt register status bit

- by ID register

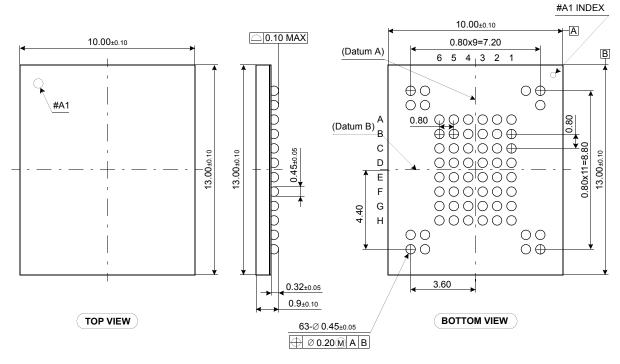

63ball, 10mm x 13mm x max 1.0mmt, 0.8mm ball pitch FBGA 63ball, 10mm x 13mm x max 1.2mmt, 0.8mm ball pitch FBGA

63ball, 10mm x 13mm x max 1.4mmt , 0.8mm ball pitch FBGA (TBD)

## 2.0 DEVICE DESCRIPTION

## 2.1 Detailed Product Description

The Flex-OneNAND is an advanced generation, high-performance MLC NAND-based Flash memory(Which can be programmed as both SLC and MLC).

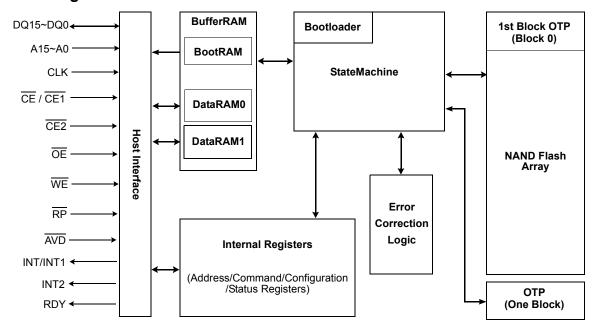

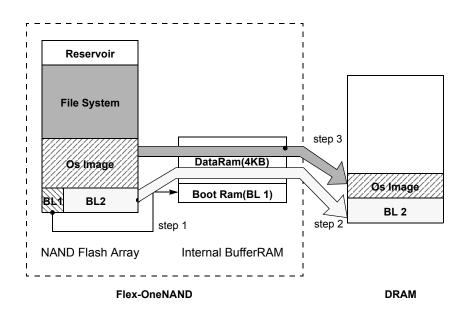

It integrates on-chip a convertible(SLC and MLC) NAND Flash Array memory with two independent data buffers, boot RAM buffer, a page buffer for the Flash array, and a one-time-programmable block.

The combination of these memory areas enable high-speed pipelining of reads from host, BufferRAM, Page Buffer, and NAND Flash Array.

Clock speeds up to 66MHz / 83MHz with a x16 wide I/O yields a 83MByte/second in SLC and 71MByte/second in MLC read bandwidth

The Flex-OneNAND also includes a Boot RAM and boot loader. This enables the device to efficiently load boot code at device startup from the NAND Array without the need for off-chip boot device.

One block of the NAND Array is set aside as an OTP memory area, and 1st Block (Block 0) can be used as OTP area. This area, available to the user, can be configured and locked with secured user information.

On-chip controller interfaces enable the device to operate in systems without NAND Host controllers.

#### 2.2 Definitions

| B (capital letter)    | Byte, 8bits                                                                                                                                     |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| W (capital letter)    | Word, 16bits                                                                                                                                    |

| b (lower-case letter) | Bit                                                                                                                                             |

| ECC                   | Error Correction Code                                                                                                                           |

| Calculated ECC        | ECC that has been calculated during a load or program access                                                                                    |

| Written ECC           | ECC that has been stored as data in the NAND Flash array or in the BufferRAM                                                                    |

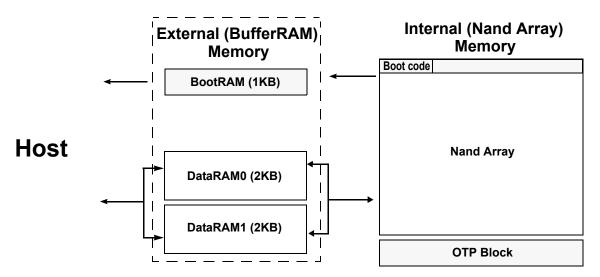

| BufferRAM             | On-chip internal buffer consisting of BootRAM and DataRAM                                                                                       |

| BootRAM               | A 1KB portion of the BufferRAM reserved for Boot Code buffering                                                                                 |

| DataRAM               | A 4KB portion of the BufferRAM reserved for Data buffering (2KB x2)                                                                             |

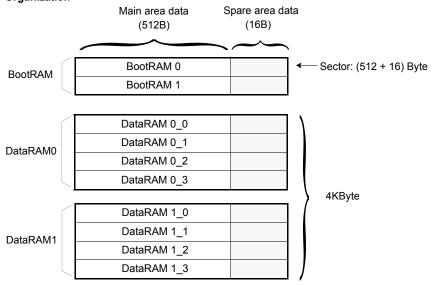

| Sector                | Part of a Page of which 512B is the main data area and 16B is the spare data area.                                                              |

| Data unit             | Possible data unit to be read from memory to BufferRAM or to be programmed to memory 4224B of which 4096 is in main area and 128B in spare area |

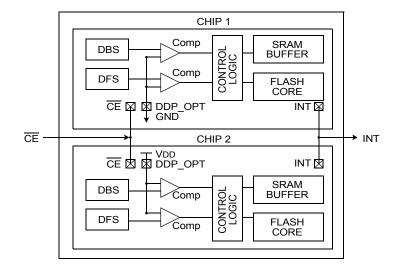

| DDP                   | Dual Die Package                                                                                                                                |

| QDP                   | Quad Die Package                                                                                                                                |

| OTP                   | One Time Programmable                                                                                                                           |

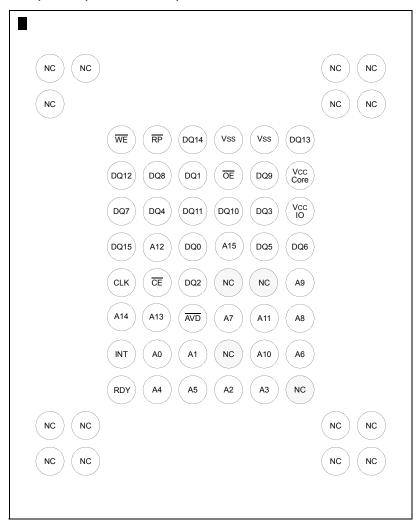

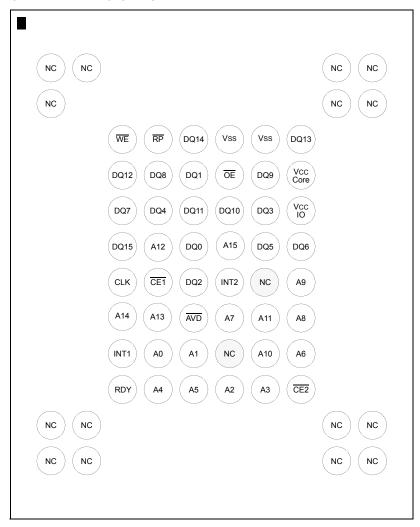

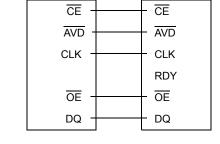

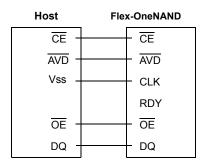

## 2.3 Pin Configuration

## 2.3.1 4Gb (KFG4GH6x4M) / 8Gb (KFH8GH6x4M)

#### (TOP VIEW, Balls Facing Down) 63ball FBGA Flex-OneNAND Chip

63ball, 10mm x 13mm x max 1.0mmt , 0.8mm ball pitch FBGA(4Gb) 63ball, 10mm x 13mm x max 1.2mmt , 0.8mm ball pitch FBGA (8Gb)

### 2.3.2 16Gb Product (KFWAGH6x4M) (TBD)

(TOP VIEW, Balls Facing Down) 63ball FBGA OneNAND Chip

63ball, 10mm x 13mm x max 1.4mmt , 0.8mm ball pitch FBGA

## 2.4 Pin Description

| Pin Name          | Туре | Nameand Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host Interface    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

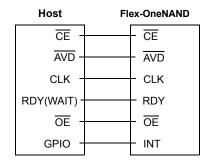

| A15~A0            | I    | Address Inputs - Inputs for addresses during read and write operation, which are for addressing BufferRAM & Register.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DQ15~DQ0          | I/O  | Data Inputs/Outputs  - Inputs data during program and commands for all operations, outputs data during memory array/ register read cycles.  Data pins float to high-impedance when the chip is deselected or outputs are disabled.                                                                                                                                                                                                                                                                                                                 |

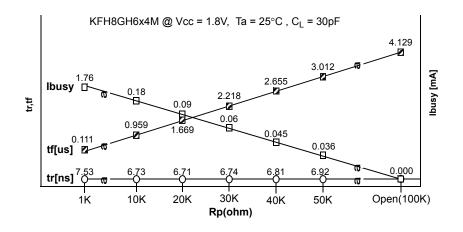

| INT / INT1        | 0    | Interrupt  Notifies the Host when a command is completed. After power-up, it is at hi-z condition. Once IOBE is set to 1, it does not float to hi-z condition even when $\overline{\text{CE}}$ is disabled or $\overline{\text{OE}}$ is disabled. Especially, only when reset(Cold, Warm, Hot, NAND Flash Core) command in DDP are issued, it operates as open drain output with internal resistor (~50Kohm). The INT is the interrupt for Single or DDP device. The INT1 is the interrupt for the first DDP device(KFH8GH6x4M) in QDP(KFWAGH6x4M) |

| INT2              | 0    | Interrupt The INT2 is the interrupt for the second DDP device(KFH8GH6x4M) in QDP(KFWAGH6x4M)                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

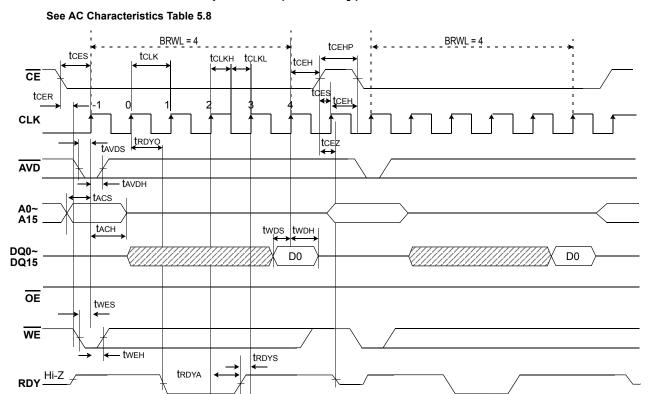

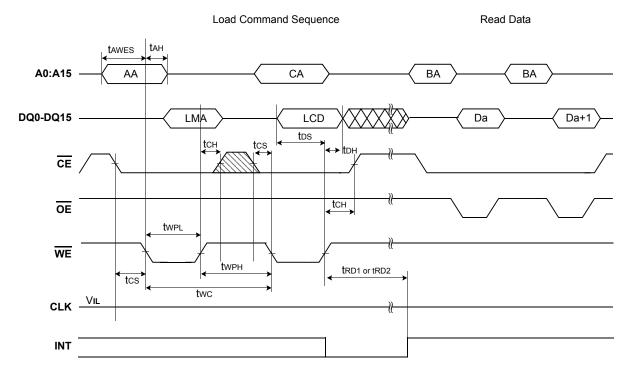

| RDY               | 0    | Ready Indicates data valid in synchronous read modes and is activated while $\overline{\text{CE}}$ is low                                                                                                                                                                                                                                                                                                                                                                                                                                          |

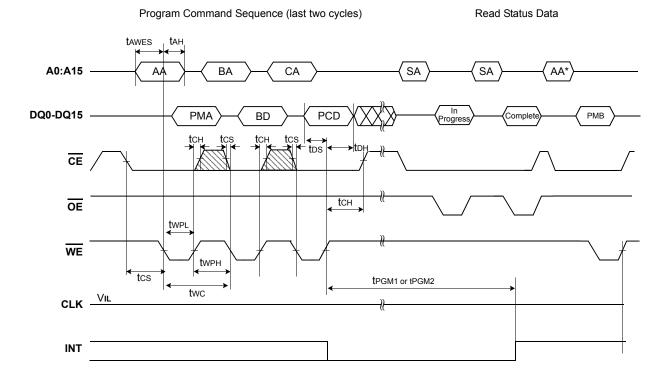

| CLK               | 1    | Clock CLK synchronizes the device to the system bus frequency in synchronous read mode. The first rising edge of CLK in conjunction with AVD low latches address input.                                                                                                                                                                                                                                                                                                                                                                            |

| WE                | I    | Write Enable WE controls writes to the bufferRAM and registers. Datas are latched on the WE pulse's rising edge                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ĀVD               | 1    | Address Valid Detect Indicates valid address presence on address inputs. During asynchronous read operation, all addresses are valid while AVD is low, and during synchronous read operation, all addresses are latched on CLK's rising edge while AVD is held low for one clock cycle.  > Low: for asynchronous mode, indicates valid address; for burst mode, causes starting address to be latched on rising edge on CLK  > High: device ignores address inputs                                                                                 |

| RP                | 1    | Reset Pin When low, RP resets internal operation of Flex-OneNAND. RP status is do not care during power-up and bootloading. When high, RP level must be equivalent to Vcc-IO / Vccq level.                                                                                                                                                                                                                                                                                                                                                         |

| CE / CE1          | ı    | Chip Enable CE-low activates internal control logic, and $\overline{\text{CE}}$ -high deselects the device, places it in standby state, and places DQ in Hi-Z. The $\overline{\text{CE}}$ input enables device for Single or DDP. The $\overline{\text{CE}}$ 1 input enables the first DDP device(KFH8GH6x4M) in QDP(KFWAGH6x4M)                                                                                                                                                                                                                   |

| CE2               | I    | Chip Enable The CE2 input enables the second DDP device(KFH8GH6x4M) in QDP(KFWAGH6x4M)                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ŌĒ                | 1    | Output Enable  OE-low enables the device's output data buffers during a read cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Power Supply      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VCC-Core<br>/ Vcc |      | Power for Flex-OneNAND Core This is the power supply for Flex-OneNAND Core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VCC-IO<br>/ Vccq  |      | Power for Flex-OneNAND I/O This is the power supply for Flex-OneNAND I/O Vcc-IO / Vccq is internally separated from Vcc-Core / Vcc.                                                                                                                                                                                                                                                                                                                                                                                                                |

| VSS               |      | Ground for Flex-OneNAND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| etc.              |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DNU               |      | Do Not Use Leave it disconnected. These pins are used for testing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NC                |      | No Connection Lead is not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### NOTE:

Do not leave power supply (Vcc-Core/Vcc-IO, VSS) disconnected.

### 2.5 Block Diagram

## 2.6 Memory Array Organization

The Flex-OneNAND architecture integrates several memory areas on a single chip.

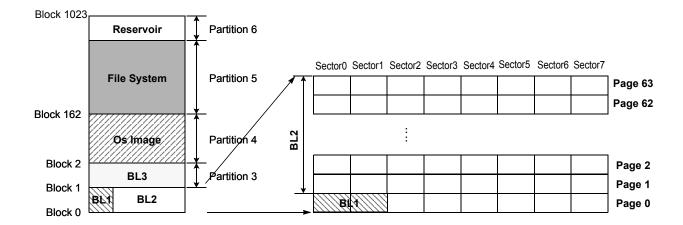

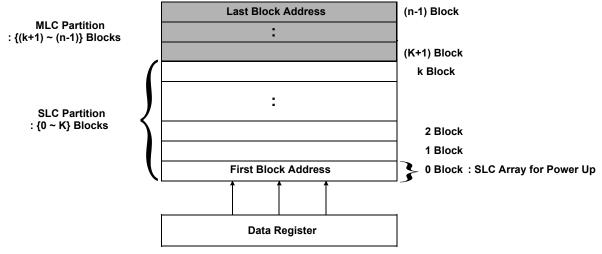

### 2.6.1 Internal (NAND Array) Memory Organization

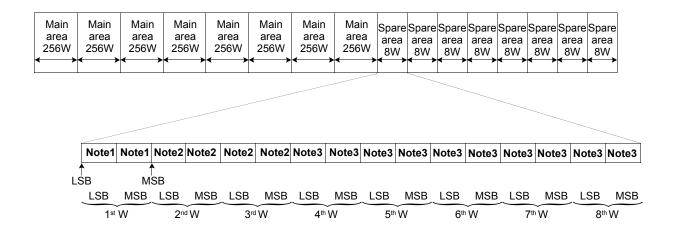

The on-chip internal memory is a convertible(SLC and MLC) NAND array used for data storage and code. The internal memory is divided into a main area and a spare area.

#### Main Area

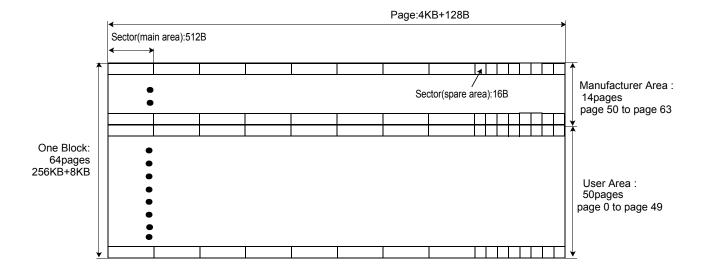

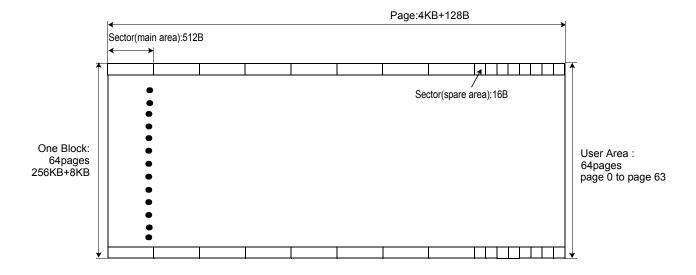

The main area is the primary memory array. A block incorporates 64pages(SLC) or 128pages(MLC). A main page size is 4KB and a main page is comprised of 8 sectors each size of which is 512Byte.

#### Spare Area

The spare area is used for invalid block information and ECC storage. Spare area internal memory is associated with corresponding main area memory. A spare page size is 128B and a spare page is comprised of 8 sectors each size of which is 16Byte.

### **Internal Memory Array Information**

| Area       | Block     | Page   | Sector |  |

|------------|-----------|--------|--------|--|

| Main(SLC)  | 256KB 4KB |        | 512B   |  |

| Main(MLC)  | 512KB     | 4ND    | 3126   |  |

| Spare(SLC) | 8KB       | 120B   | 16B    |  |

| Spare(MLC) | 16KB      | - 128B | 105    |  |

### **Internal Memory Array Organizatio**

| Sector<br>Main Area      | I<br>Spare Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 512B                     | 16B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ]                |

|                          | <br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1<br>            |

| <b>Page</b><br>Main Area | Spare Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  |

|                          | Sector() Sector() Sector(2 Sector(3 Sector(4 Sector(5 Sector(6 Sec | ]                |

| 4KB(512Bx8)              | 128B(16Bx8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ]                |

| 1                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |

| Block(MLC)               | i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |

| Main Area                | Spare Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7                |

| 4KB Page0                | 128B Page0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page 0           |

|                          | • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ;<br>;<br>;      |

| 4KB Page127              | 128B Page127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page 127         |

| 512KB                    | 16KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <del> </del><br> |

|                          | ]<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |

| Block(SLC)               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |

| Main Area                | Spare Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  |

| 4KB Page0                | 128B Page0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page 0           |

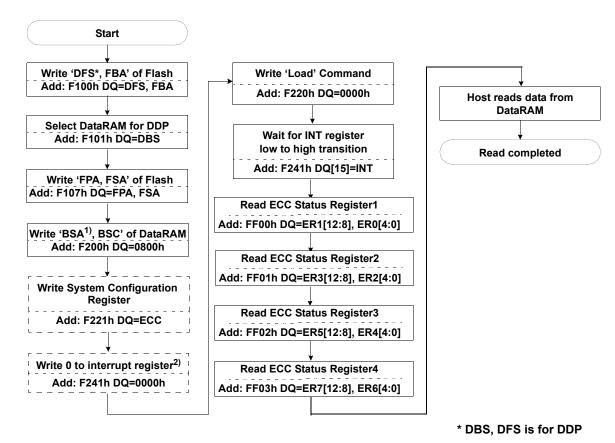

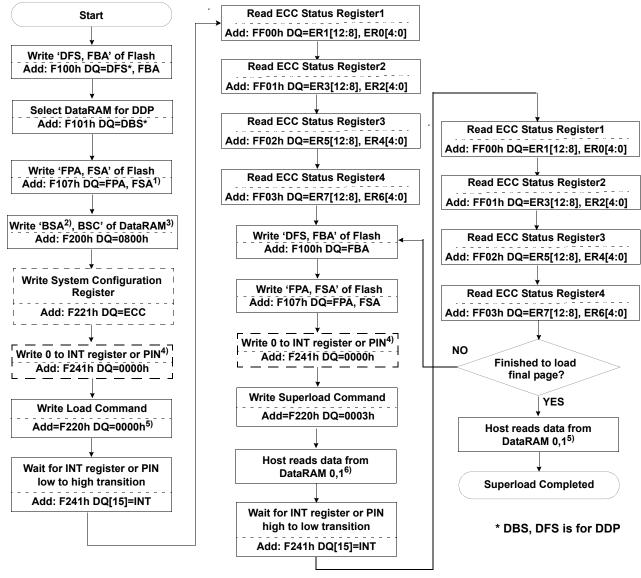

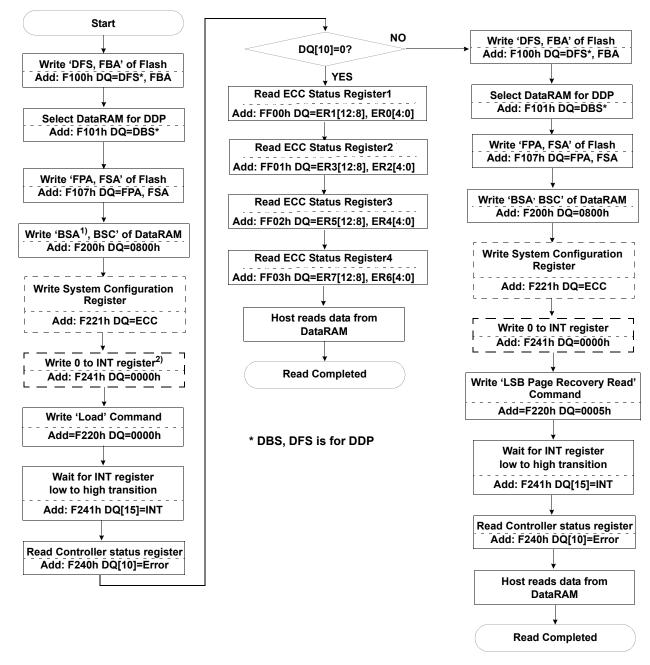

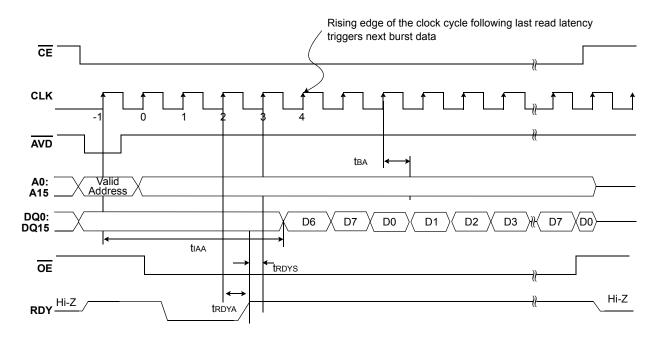

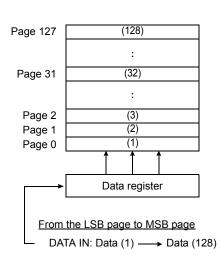

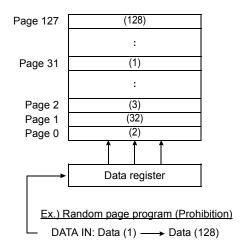

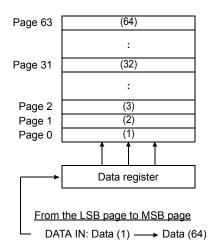

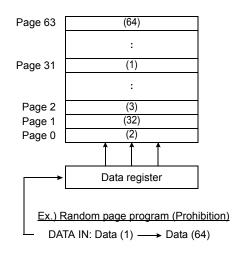

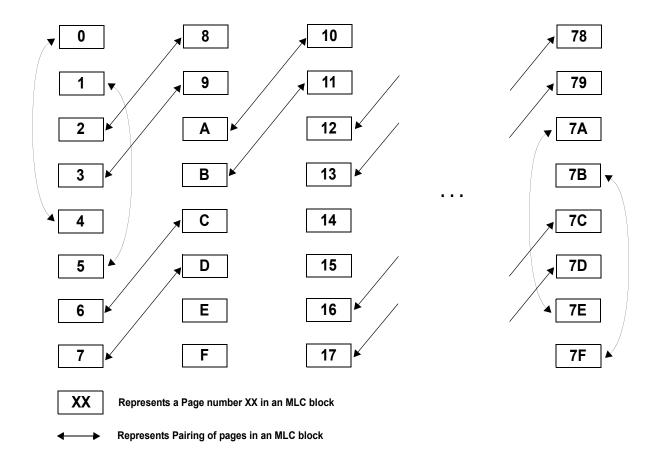

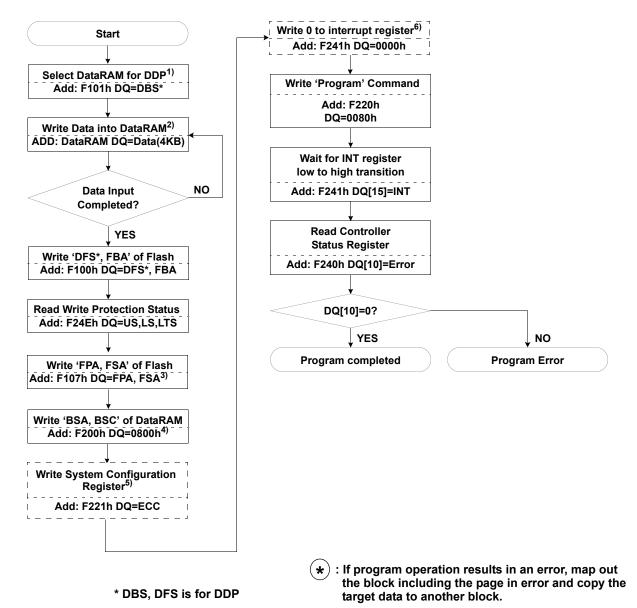

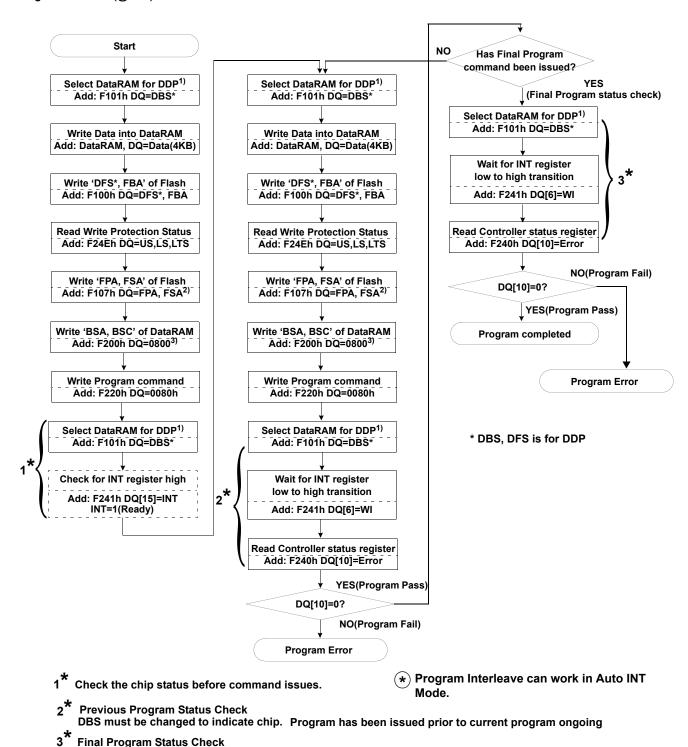

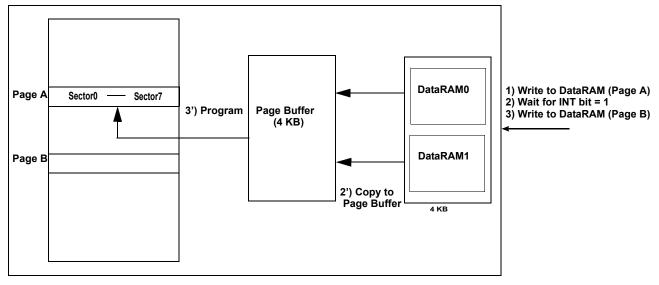

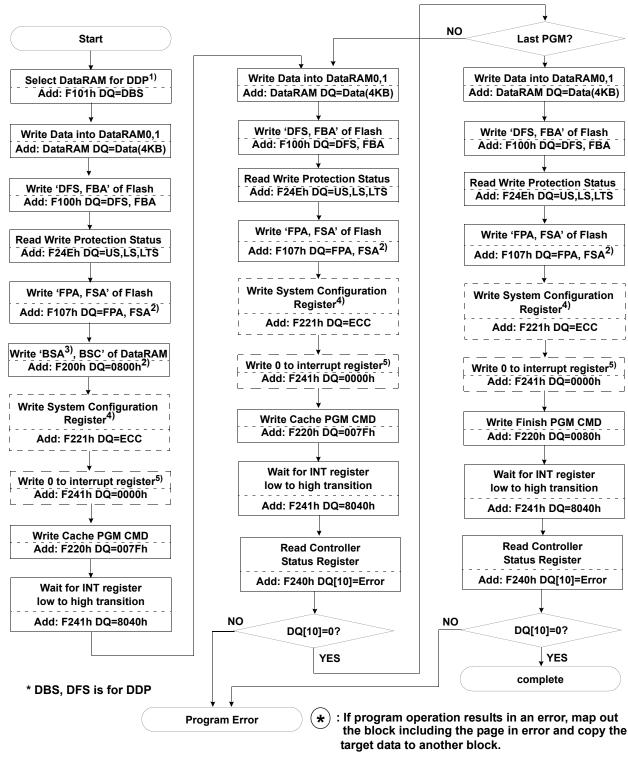

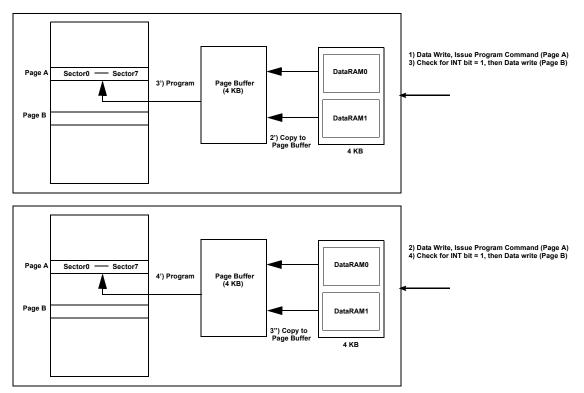

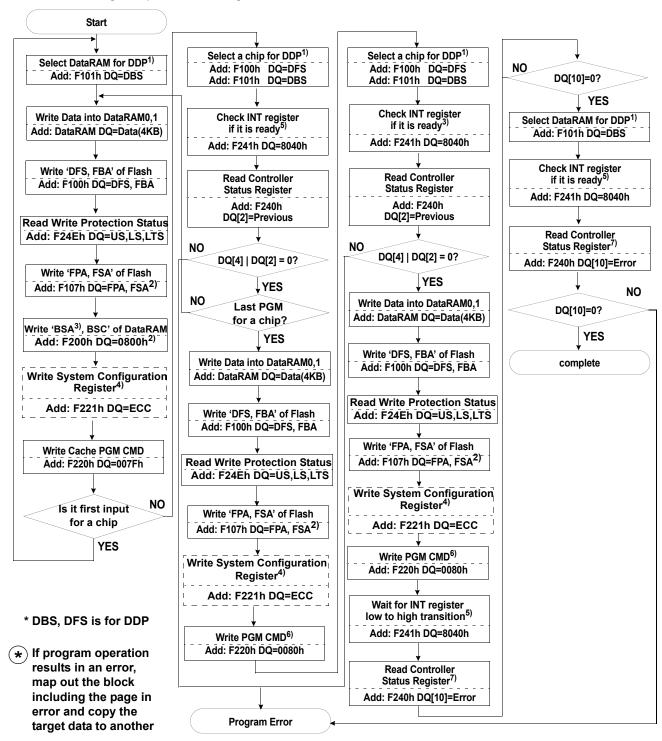

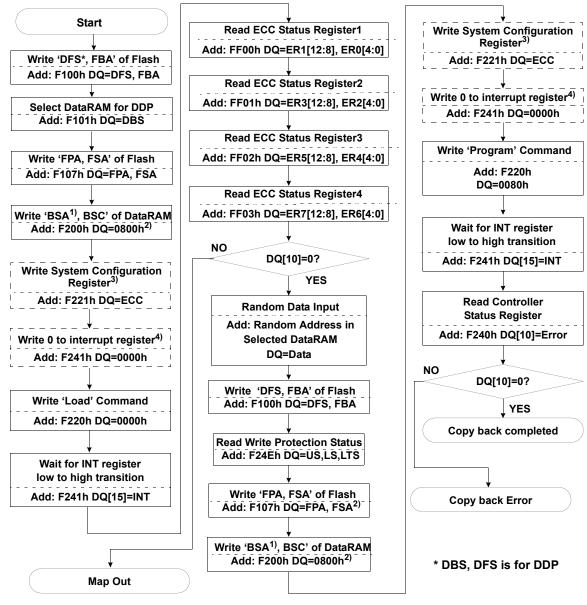

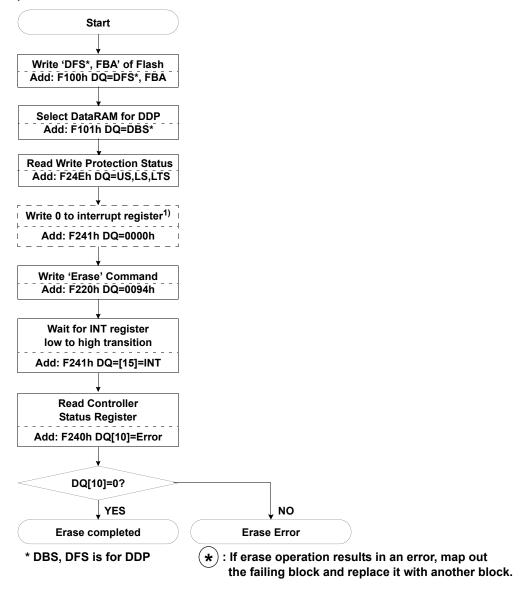

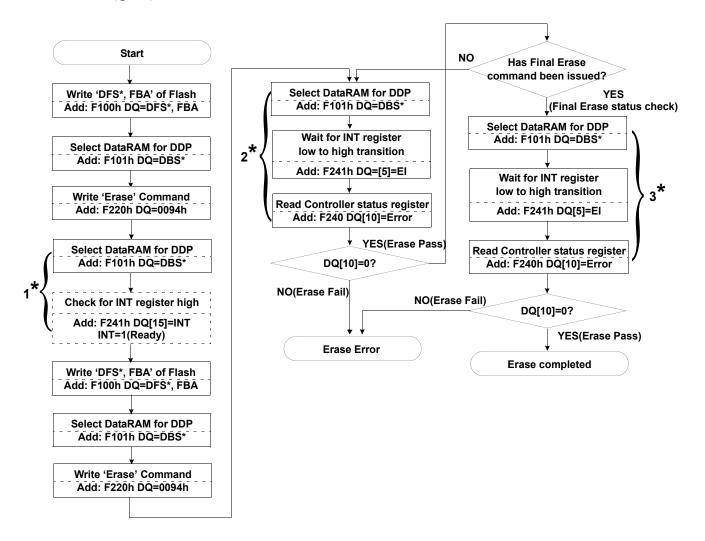

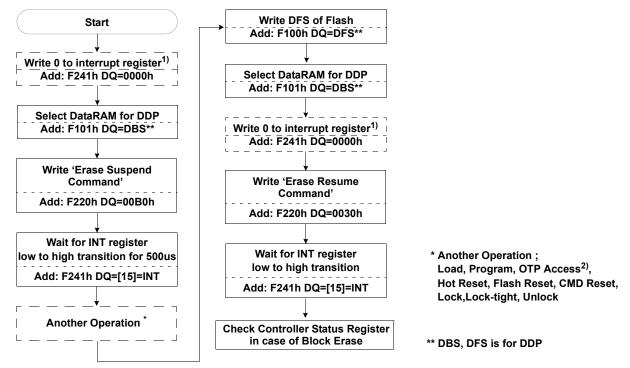

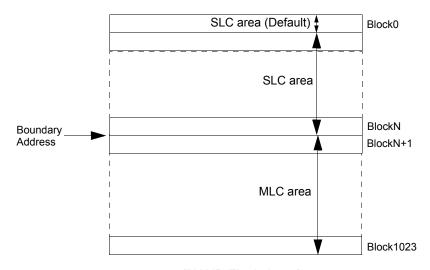

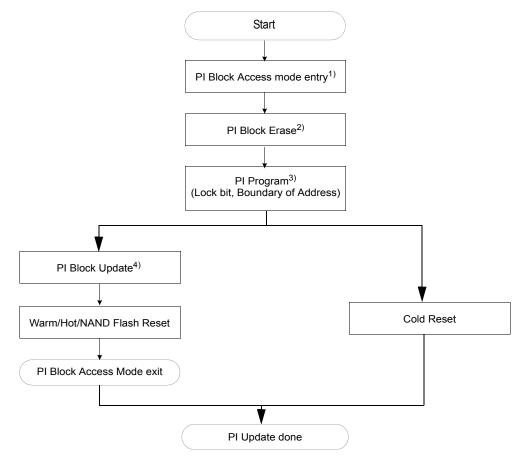

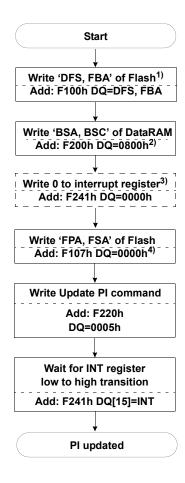

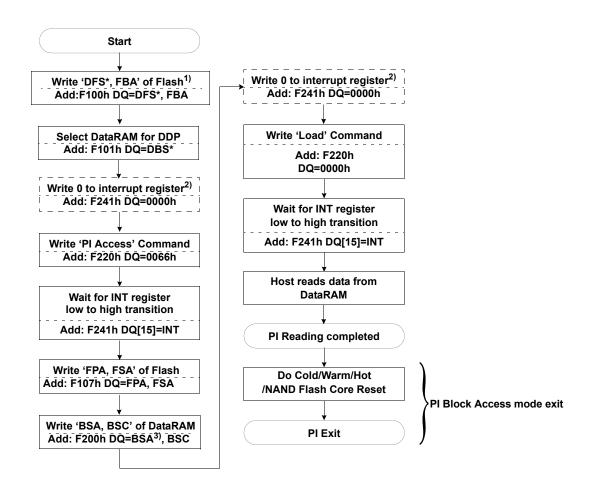

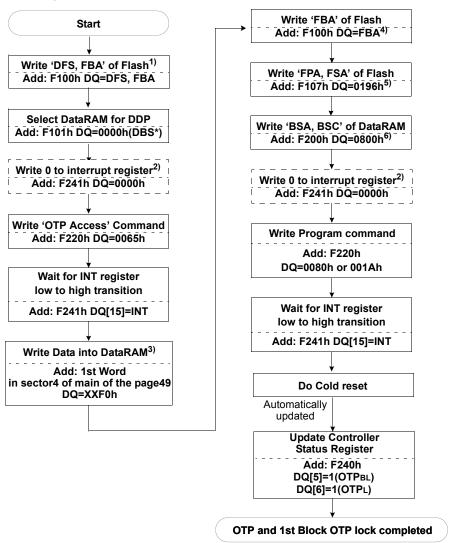

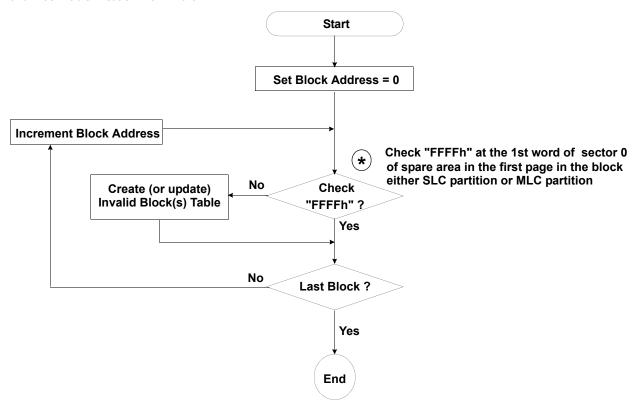

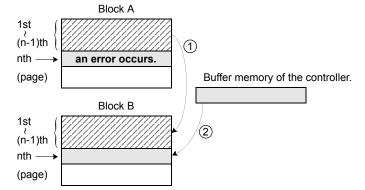

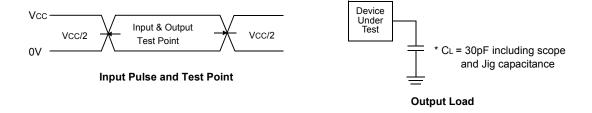

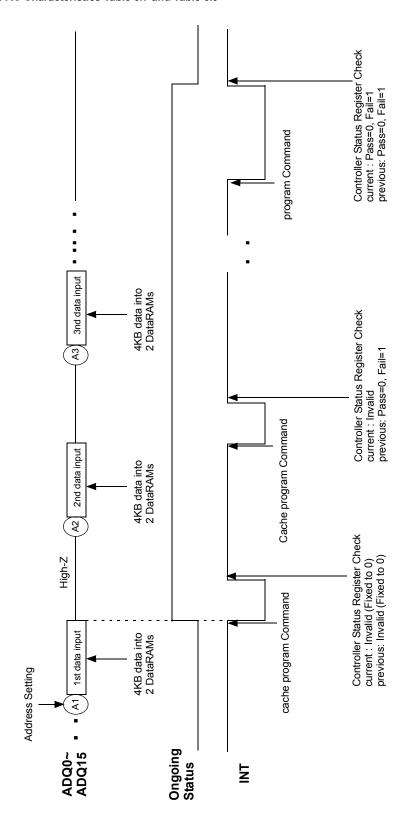

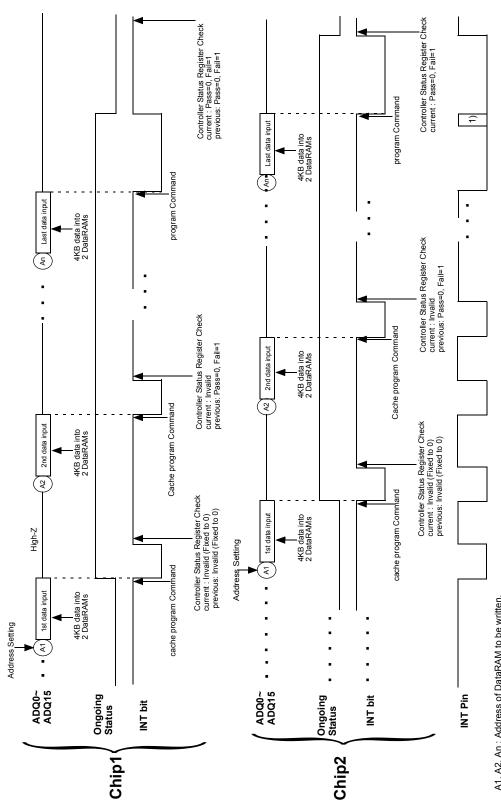

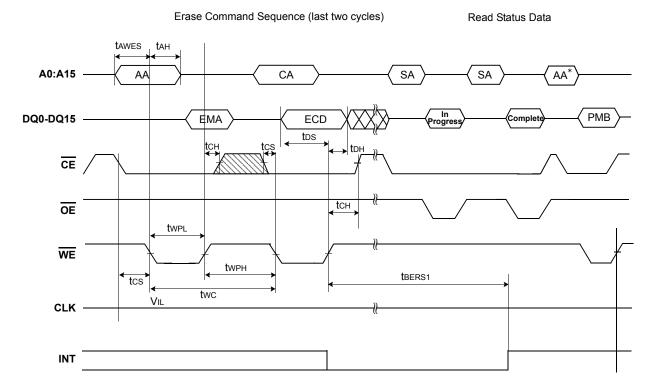

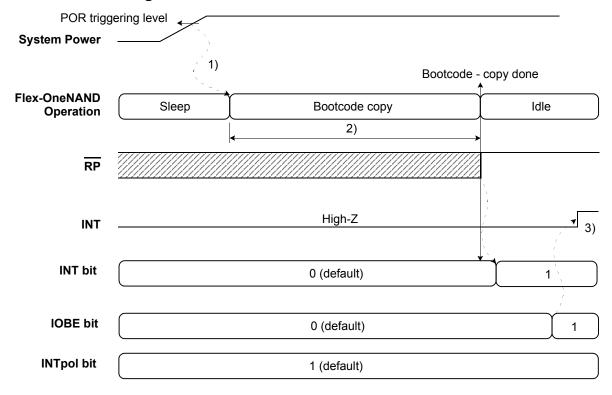

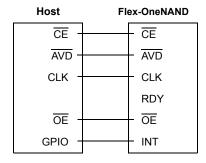

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •                |